Project Info

The Megapixel Motion IP core is a video analytic core for on-line hardware background calculation with optimized feature for motion vector extraction and filtering.

Description

The Megapixel Motion IP core is a video analytic core for on-line hardware background calculation with optimized feature for motion vector extraction and filtering.

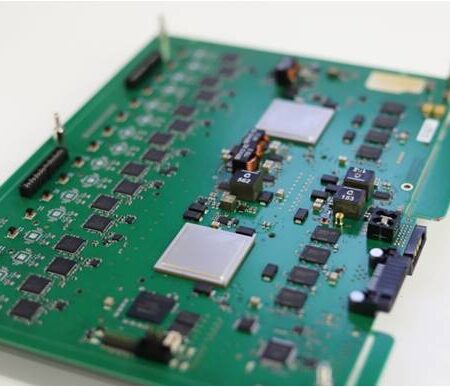

This core is optimized for FPGAs and require external video buffer memory. It operate at pixel rate up to 98 MHz for FPGA version on the IP camera board. Resource required include 2 dual port memory for image linear buffering to optimize memory access and 7 DSP element for multiplication element (ref XP2 DSP sum-multiply 18 bit block). The core is supported by application example based on LINUX OS.

| Resource Utilization Lattice XP2™ |

|||

|---|---|---|---|

| EBR | LUT | Register | Fmax(MHz) |

| 2 | 1053 | 1290 | 125 |

Key Features

- On Line static background calculation

- RGB and Monochromatic version

- Compressed output

- Linear or 2D optional output filtering

- Reduced PC CPU occupancy

- Programmable background update speed

- Programmable sensitivity

- Selectable motion mask grid

Technical Description

The Megapixel Motion IP capture current frame from the sensor IF and fetch the registered images from the memory to calculate the current image background and extract the movement vector. The active image area can be configured with a user selectable selection grid (Motion Mask). Sensitivity and time related parameters can be user configured to accommodate several motion related alarms.

Motion IP memory access requirements:

- Current frame (also from sensor bus)

- Two registered frame (Read)

- Previous background image (Read)

- Updated background image (Write)

- Movement vector (Write)

Final memory mapped video buffer and related memory bandwidth depend on selected resolution and can be configured in the IP core register interface.

Software Library

- Linux register interface

- User application GUI

- EVM board FPGA based (Megapixel IP camera)